塑膠原料 連接工業(yè)與情感,見證每一份終成眷屬

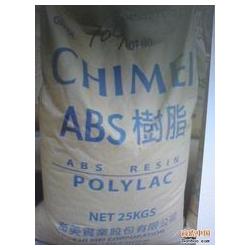

在現(xiàn)代化工業(yè)的龐大體系中,塑膠原料扮演著不可或缺的基礎(chǔ)角色。從我們?nèi)粘J褂玫碾娮赢a(chǎn)品外殼、汽車零部件,到醫(yī)療器具、食品包裝,塑膠材料以其輕質(zhì)、耐用、可塑性強(qiáng)及成本效益高等特點,滲透到生產(chǎn)與生活的方方面面。而塑膠原料的生產(chǎn),更是一門融合了化學(xué)工程、材料科學(xué)與精密制造的技術(shù),旨在通過聚合等工藝,將石油或天然氣中的單體轉(zhuǎn)化為性能各異的聚合物,滿足下游產(chǎn)業(yè)千變?nèi)f化的需求。

在這一專業(yè)而嚴(yán)謹(jǐn)?shù)墓I(yè)領(lǐng)域背后,同樣流淌著人文的溫暖。正如“覲銘塑膠原料”所祝愿的——“祝有情人終成眷屬”,這不僅是對于美好情感的祝福,也隱喻了塑膠原料與終端產(chǎn)品之間、供應(yīng)商與客戶之間,乃至創(chuàng)新技術(shù)與市場需求之間,那種尋求完美匹配、和諧共生的“聯(lián)姻”關(guān)系。每一批高品質(zhì)的塑膠原料,都像是經(jīng)過精心準(zhǔn)備的“聘禮”,等待著被加工、塑造,最終成為一件有價值的產(chǎn)品,完成其工業(yè)使命。

因此,當(dāng)我們談?wù)撍苣z原料與塑膠材料時,我們不僅是在探討其物理性能、環(huán)保改性或市場趨勢,也是在欣賞一種連接物質(zhì)與情感、理性與感性的獨特紐帶。它默默支撐著現(xiàn)代社會的運轉(zhuǎn),也默默祝福著每一個追求完美結(jié)合的故事——無論是在工廠的生產(chǎn)線上,還是在人們的生活里。愿每一份匠心與真誠,都能如優(yōu)質(zhì)的塑膠材料般,歷久彌新,終成眷屬。

如若轉(zhuǎn)載,請注明出處:http://www.haiyuhotel.com.cn/product/2.html

更新時間:2026-03-07 14:18:12